컴퓨터가 이해하는 정보

데이터와 명령어

- 컴퓨터가 직접 이해할 수 있는 것: 오직 데이터(Data)와 명령어(Instruction)

- 데이터: 숫자(정수, 실수), 문자, 이미지, 영상 등 ‘정적 정보’를 의미. 명령어가 어떻게 처리할지 결정되는 ‘대상’

- 명령어: 수행할 동작(Operation)과 수행할 대상(Operand)으로 구성

- CPU가 이 명령어를 처리하고, 메모리 등 저장장치에 있는 데이터를 참조하여 프로그램을 실행함

0과 1의 세계

- 컴퓨터 내부에서 모든 정보는 0과 1로 표현됨

- 가장 작은 정보 단위를 비트(bit) 라고 하며, 8개 비트를 묶은 것을 바이트(byte) 라고 함

- 용량 단위:

1KB = 1000B,1MB = 1000KB,1GB = 1000MB…

→ 실제 컴퓨터에서는 2진수 기반: 1KiB = 1024B(Kibibyte), 1MiB = 1024KiB(Mebibyte) 등

kibibyte(키비바이트), mebibyte(메비바이트) 식으로 읽음

- 워드(Word): CPU가 한 번에 처리할 수 있는 데이터의 크기

- 예: 32비트 CPU는 한 번에 32비트 처리 → 32bit 워드 크기

숫자 표현(2진법, 16진법, 부동소수점)

- 2진법

- 16진법

1010(10진수 10)은 16진수 A로 표현

- 부동소수점 (Floating Point)

1.23123 × 10^2에서 정수 부분(가수, Mantissa)과 지수(Exponent)로 구성

문자 표현(ASCII, 유니코드, Base64)

- ASCII

- EUC-KR

- 유니코드(Unicode)

- Base64

= 등을 패딩 문자로 사용

컴퓨터의 핵심 부품

CPU

- 중앙 처리 장치(Central Processing Unit)

- 명령어를 인출(Fetch), 해석(Decode), 실행(Execute) 하는 핵심 부품

- 내부 구성 요소

1. 산술논리연산장치(ALU): 실제 연산(덧셈, 뺄셈, 논리연산 등)을 수행

2. 제어장치(Control Unit): 각 부품에 제어 신호를 보내어 동작을 지휘

3. 레지스터(Register): 연산 과정에서 발생하는 임시 데이터를 저장하는 초고속 메모리

메모리와 캐시 메모리

- 메인 메모리(주기억장치)

- 캐시 메모리(Cache Memory)

보조기억장치

- 비휘발성 저장장치

- HDD, SSD 등이 대표적

- 프로그램이나 데이터를 영구적으로 저장하기 위한 용도

- CPU가 직접 읽고 실행할 수 없으므로, 사용 시 메모리에 복사 후 CPU가 처리

입출력장치

- 마우스, 키보드, 마이크(입력) / 모니터, 스피커, 프린터(출력) 등

- 이들을 주변장치(Peripheral) 라고 통칭

메인보드와 버스

- 메인보드(마더보드): CPU, 메모리, 주변장치 등을 물리적으로 연결하는 기판

- 버스(Bus): 각 부품 간에 데이터를 주고받는 전송 통로

- 예) 시스템 버스: CPU, 메모리, 주변장치를 연결하는 중요한 버스

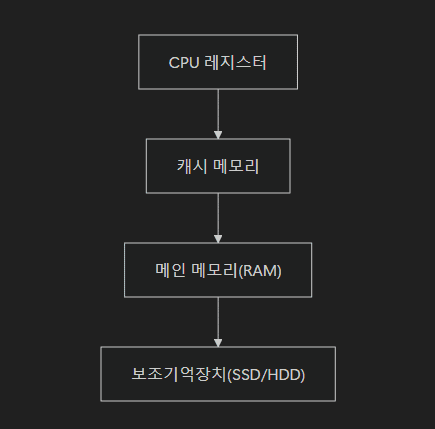

저장장치 계층 구조

아래는 CPU 관점에서 가까울수록 빠르지만 용량이 작고, 멀수록 느리지만 용량이 크며 가격이 저렴한 구조입니다.

- 가까울수록(레지스터, 캐시) 속도가 빠르고 용량이 작으며 비쌈

- 멀수록(보조기억장치) 속도가 느리고 용량이 크며 저렴

명령어

명령어의 구성

- 연산 코드(OpCode): 무엇을 할 것인지(어떤 연산을 수행?)

- 오퍼랜드(Operand): 연산에 사용될 데이터 혹은 데이터의 메모리 주소(또는 레지스터)

- 예)

ADD R1, R2→ADD는 연산 코드,R1, R2는 오퍼랜드

기계어와 어셈블리어

- 기계어(Machine Language): CPU가 직접 해석할 수 있는 0과 1의 명령어

- 어셈블리어(Assembly Language): 기계어를 사람이 이해하기 조금 쉽게 명령어 형태로 표기한 언어

- 기계어와 1:1로 대응

- CPU 종류마다(명령어 집합 구조마다) 다름 → 호환성 주의

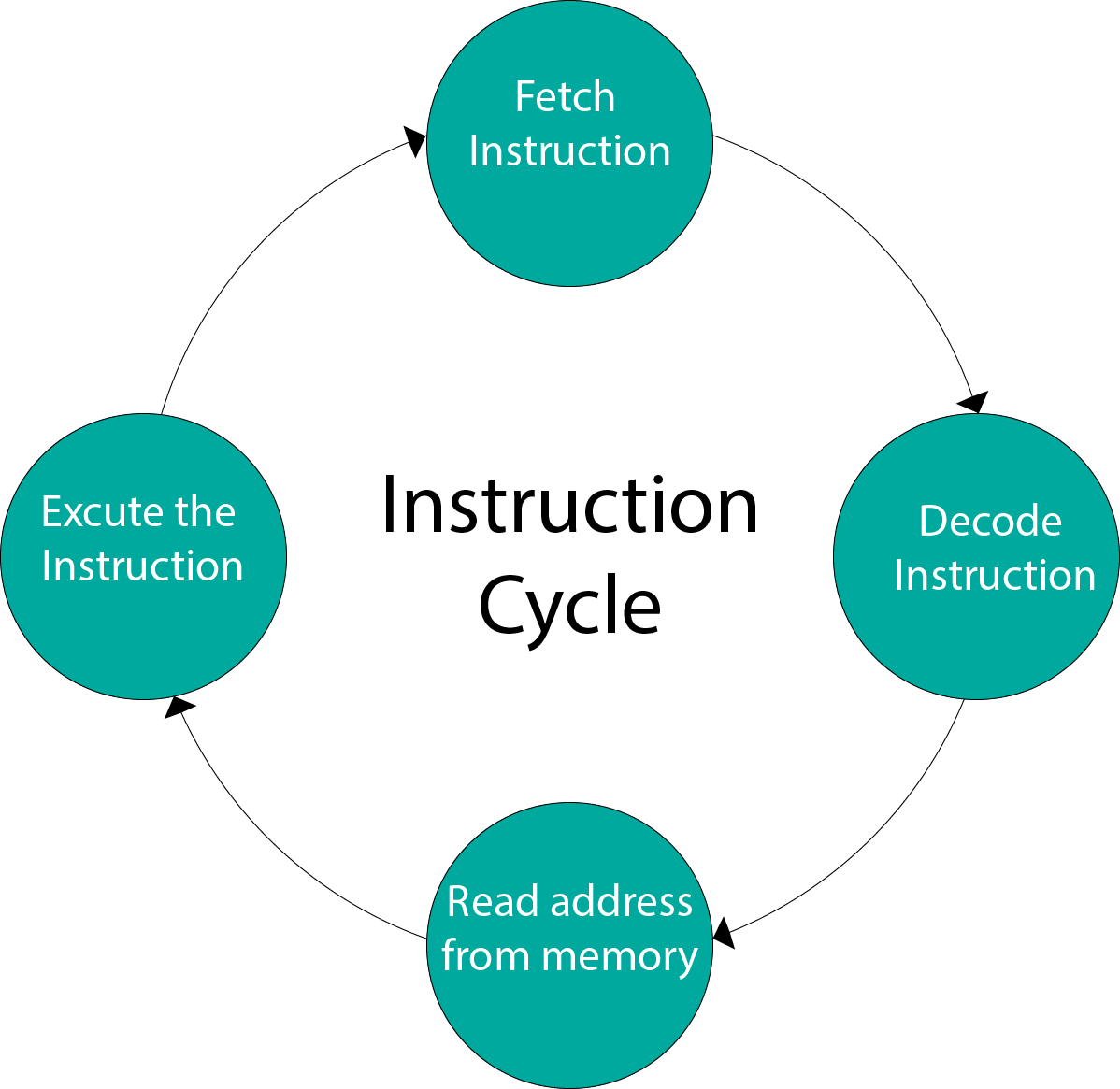

명령어 사이클

CPU가 명령어를 처리하는 순서(주기)로, 일반적으로 아래 단계를 반복합니다.

- 인출 사이클(Fetch cycle)

- 간접 사이클(Indirect cycle)

- 실행 사이클(Execute cycle)

- 인터럽트 사이클(Interrupt cycle)

CPU 구체적으로 살펴보기

레지스터

CPU 내부에는 다양한 레지스터가 존재하며, 각각 용도에 따라 이름과 역할이 달라집니다.

- 프로그램 카운터(PC, Program Counter)

- 명령어 레지스터(IR, Instruction Register)

- 범용 레지스터(General-Purpose Register)

- 플래그 레지스터(Flag Register)

Zero Flag(결과가 0이면 1), Carry Flag, Overflow Flag, Sign Flag 등

- 스택 포인터(Stack Pointer)

인터럽트와 예외

- 인터럽트(Interrupt)

1. 인터럽트 신호 발생

2. CPU는 명령어 사이클 단위로 인터럽트 발생 여부 확인

3. 인터럽트 가능 여부(플래그) 확인 → 가능하면 현재 레지스터 상태 백업

4. ISR 실행

5. ISR 종료 후, 백업해둔 상태를 복구하고 원래 작업 재개

- 예외(Exception)

CPU 성능 향상을 위한 설계

클럭 속도

- 클럭(Clock): CPU 및 주변 장치가 동작할 때 기준이 되는 타이밍 신호

- 헤르츠(Hz): 1초에 몇 번 클럭이 반복되는지 나타내는 단위

- 3GHz CPU → 1초에 30억 번의 클럭

- 클럭 속도가 높을수록, CPU가 명령어 사이클을 더 빠르게 반복할 것으로 기대

멀티 코어와 멀티 스레드

멀티 코어(Multi-Core)

- CPU 내부에 ‘코어’라는 명령어 처리 유닛을 여러 개 탑재

- 예) 8코어 CPU → 내부에 독립된 CPU 8개가 있는 셈

- 한 번에 여러 개의 스레드를 병렬(Parallel) 처리 가능

멀티 스레드(Multi-Thread)

- 하나의 코어가 동시에 여러 실행 흐름(스레드)을 처리하도록 설계

- 예) 2코어 4스레드 CPU → 논리적으로는 코어가 4개 있는 것처럼 동작 (하이퍼스레딩, SMT 등)

하드웨어 스레드 vs 소프트웨어 스레드

| 구분 | 하드웨어 스레드 (Hardware Thread) | 소프트웨어 스레드 (Software Thread) |

|---|---|---|

| 정의 | CPU 내부에서 동시에 실행될 수 있는 실행 흐름 | OS 또는 프로그램에서 관리하는 실행 단위 |

| 기반 | 물리적(Physical) 스레드 | 논리적(Logical) 스레드 |

| 실행 방식 | 실제로 CPU에서 병렬 처리(병렬성) | CPU가 빠르게 스위칭하면서 실행(동시성) |

| 예시 | 2코어 4스레드 CPU → 논리적으로 4개의 CPU처럼 보임 | 자바의 Thread 클래스, 파이썬의 threading 라이브러리 |

| 병렬성 여부 | 병렬 처리 가능 | 병렬이 아니라 동시성(Concurrency) |

| 대표 기술 | 하이퍼스레딩 (Hyper-Threading, SMT) | 멀티스레딩 (Multi-Threading, Green Threads) |

병렬성과 동시성

- 병렬성 (Parallelism):

- 물리적으로 여러 코어에서 동시에 작업을 처리

- 예) 4코어 CPU가 각각 다른 연산을 동시에 실행

- 동시성 (Concurrency):

- 실제로는 하나의 코어가 빠르게 스위칭하면서 실행하지만, 사용자 입장에서는 ‘동시에’ 처리되는 것처럼 보임

- 예) 싱글 코어에서 여러 소프트웨어 스레드를 실행하는 경우

명령어 병렬 처리(파이프라이닝, 슈퍼스칼라)

- 파이프라이닝(Pipelining)

- 명령어 처리 단계를 분할하여, 여러 명령어를 겹쳐서 처리

- 4단계 예:

인출(Fetch) → 해석(Decode) → 실행(Execute) → 결과 저장(Write Back) - 한 단계가 끝난 뒤 바로 다음 명령어를 인출해서 CPU가 쉬지 않고 계속 작업

- 현대 CPU는 더 세밀하게 나눈 파이프라인 + 여러 파이프라인(슈퍼스칼라) 적용

- 파이프라인 위험(Pipeline Hazard)

1. 데이터 위험(Data Hazard): 앞 명령어의 결과를 아직 저장 안 했는데 뒤 명령어가 가져다 쓰려고 할 때

2. 제어 위험(Control Hazard): 분기나 점프 명령어로 인해 파이프라인에 이미 인출된 명령어가 무효화

3. 구조적 위험(Structural Hazard): 동시에 실행 중인 명령어들이 같은 하드웨어 자원을 쓰려 할 때 충돌

- 슈퍼스칼라(Superscalar)

- CPU 내부에 여러 파이프라인을 병렬로 배치

- 한 사이클에 여러 명령어를 동시에 실행할 수 있도록 설계

CISC vs RISC

- CISC(Complex Instruction Set Computer)

- 복잡하고 다양한 명령어를 적게 호출해서 일을 처리하는 방식

- 하나의 명령어가 여러 클럭 사이클 필요 (가변 길이, 가변 실행 시간)

- 인텔의 x86 아키텍처가 대표적

- RISC(Reduced Instruction Set Computer)

- 명령어 종류와 형식을 단순화하고, 대부분의 명령어가 1클럭(또는 소수 클럭) 내에 실행되도록 설계

- 파이프라이닝 효율이 높음

- 애플의 M1, ARM 계열 프로세서 등이 대표적

핵심 포인트

- 컴퓨터는 오직 0과 1로 된 정보를 이해하며, 모든 데이터(숫자, 문자 등)는 2진수로 표현

- CPU가 명령어를 인출하고(PC), 해석하여(IR), 실행(ALU)하고 결과를 다시 레지스터/메모리에 저장

- 인터럽트는 CPU에 작업을 ‘잠시 멈추고 다른 작업을 처리하라’는 신호

- CPU 성능을 높이기 위한 대표적 방법: 클럭 상승, 멀티 코어/스레드, 파이프라이닝, 슈퍼스칼라, RISC 구조 등

참고

이것이 취업을 위한 컴퓨터 과학이다 with CS 기술 면접 – 한빛미디어